# S1K50000 Series DESIGN GUIDE

# NOTICE No part of this material may be reproduced or duplicated in any from or by any means without the written permission of EPSON. EPSON reserves the right to make changes to this material without notice. EPSON does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this marerial will be free from any patent or copyright infringement of a third party. This material or portions there of may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. ©SEIKO EPSON CORPORATION 2001, All rights reserved.

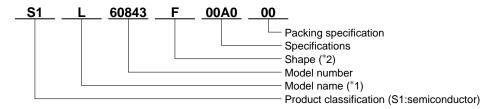

# New configuration of product number

Starting April 1, 2001 the configuration of product number descriprions will be changed as listed below. To order from April 1, 2001 please use these product numbers. For further information, please contact Epson sales representative.

# Configuration of product number

# DEVICES

#### \*1: Model name

| Κ | Standard Cell  |

|---|----------------|

| L | Gate Array     |

| Χ | Embedded Array |

#### \*2 : Shape

| B | Assembled on board, COB, |

|---|--------------------------|

|   | BGA                      |

| С | Plastic DIP              |

| D | Bare Chip                |

| F | Plastic QFP              |

| Н | Ceramic DIP              |

| L | Ceramic QFP              |

| М | Plastic SOP          |

|---|----------------------|

| R | TAB-QFP              |

| Т | Tape Carrier (TAB)   |

| 2 | TSOP (Standard Bent) |

| 3 | TSOP (Reverse Bent)  |

|   |                      |

# S1K50000 Series Table of Contents

| Chapter 1 Overview                                                    | 1  |

|-----------------------------------------------------------------------|----|

| 1.1 Features                                                          |    |

| 1.2 Electrical Characteristics                                        | 2  |

| 1.3 Outline of Standard-Cell Development Flow                         | 8  |

| Chapter 2 Precautions on Circuit Design                               | 10 |

| 2.1 Insertion of Input/Output Buffers                                 |    |

| 2.2 Use of Differentiating Circuits Inhibited                         |    |

| 2.3 Wired Logic Inhibited                                             |    |

| 2.4 Hazard Protection                                                 |    |

| 2.5 Fan-Out Limitations                                               |    |

| 2.6 Internal Bus Circuits                                             |    |

| 2.7 Bus Hold Circuits                                                 |    |

| 2.8 Precautions on Creating Circuit Diagrams (Logic Diagrams)         |    |

| 2.9 Clock Tree Synthesis                                              |    |

| 2.10 ATPG (Auto Test-Pattern Generation)                              |    |

| 2.11 Limitations and Restrictions on VHDL and Verilog-HDL Netlists    |    |

| 2.11.1 Common                                                         | 30 |

| 2.11.2 Limitations and Restrictions on Verilog-HDL Netlists           |    |

| 2.11.3 Limitations and Restrictions on VHDL Netlists                  |    |

| Chapter 3 Types of Input/Output Buffers and Usage Precautions         |    |

| 3.1 Types of Input/Output Buffers                                     |    |

| 3.1.1 Selecting Input/Output Buffers                                  |    |

| 3.2 Input/Output-Buffer Configuration with a Single Power Supply      |    |

| 3.2.1 Input/Output-Buffer Configuration with a Single Power Supply    | 35 |

| 3.2.1.2 Output-Buffer Configuration with a Single Power Supply        |    |

| 3.2.1.3 Bidirectional-Buffer Configuration with a Single Power Supply |    |

| 3.2.2 Fail-Safe Cells                                                 |    |

| 3.3 Configuration of Oscillator Circuits                              |    |

| 3.3.1 When Configuring an Oscillator Circuit                          |    |

| 3.3.2 Precautions on the Use of Oscillator Circuits                   |    |

| 3.4.1 Outline of Gated I/O Cells                                      |    |

| 3.4.2 Features of Gated I/O Cells                                     |    |

| 3.4.3 Precautions on the Use of Gated I/O Cells                       |    |

| Chapter 4 Circuit Design Taking Testability into Account              |    |

| 4.1 Consideration for Circuit Initialization                          |    |

| 4.2 Consideration for Reduction of the Test-Pattern Size              |    |

| 4.3 Circuit Configuration to Facilitate DC and AC Tests               |    |

| 4.3.1 Configuration of a Test Circuit                                 |    |

| 4.4 Test Circuit for Functional Cells                                 | 62 |

| 4.4.1 Configuration of a Test Circuit                                 |    |

| 4.4.2 Test Patterns                                                   |    |

| 4.4.3 Test-Circuit Information                                        |    |

| Chapter 5 Propagation Delay Time and Timing Design                    |    |

| 5.1 Precautions Regarding the Relationship between Ta and Tj          |    |

| 5.2 Simplified Delay Models                                           |    |

| 5.3 Load Due to Input Capacitance (Load A)                            |    |

| 5.4 Load Due to Wiring Capacitance (Load B)                           |    |

| 5.5 Calculating the Propagation Delay Time                            | 68 |

| 5.6 Calculating the Output-Buffer Delay Time                                  | 70  |

|-------------------------------------------------------------------------------|-----|

| 5.7 Flip-Flop Setup and Hold Times                                            | 70  |

| 5.8 Differentiating Cell Usage                                                | 73  |

| 5.9 Intra-Chip Skew                                                           | 73  |

| Chapter 6 Creating Test Patterns                                              | 74  |

| 6.1 Testability Consideration                                                 |     |

| 6.2 Usable Waveform Modulation                                                |     |

| 6.3 Limitations on Test Patterns                                              |     |

| 6.3.1 Test Rate and the Number of Events                                      |     |

| 6.3.2 Input Delay                                                             |     |

| 6.3.3 Pulse Width                                                             | 75  |

| 6.3.4 Input-Waveform Format                                                   | 75  |

| 6.3.5 Strobe                                                                  |     |

| 6.4 Precautions Regarding DC Test                                             |     |

| 6.5 Precautions on Use of an Oscillator Circuit                               |     |

| 6.6 Regarding the AC Test                                                     |     |

| 6.6.1 Restrictions on Measurement Events                                      |     |

| 6.6.2 Restrictions on AC Test Measurement Points                              |     |

| 6.6.3 Restrictions on Delays in the Measured Path                             |     |

| 6.7 Restrictions on Test Patterns for Bidirectional Pins                      |     |

| 6.8 Precautions on Handling of the High-Impedance State                       |     |

|                                                                               |     |

| Chapter 7 Estimating Power Consumption                                        |     |

| 7.1 Calculating Power Consumption                                             |     |

| 7.2 Limitations on Power Consumption                                          |     |

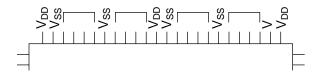

| Chapter 8 Pin Arrangement and Simultaneous Operation                          | 88  |

| 8.1 Estimating the Number of Power-Supply Pins                                |     |

| 8.2 Simultaneously Operating Buffers and Added Power Supply                   | 88  |

| 8.3 Precautions on Pin Arrangement                                            | 91  |

| 8.3.1 Fixed Power-Supply Pins                                                 |     |

| 8.3.2 Precautions on Pin Arrangement                                          |     |

| 8.3.3 Example of the Recommended Pin Arrangement                              |     |

| Chapter 9 Precautions on the Use of Dual Power Supplies                       |     |

| 9.1 Power-Supply Accommodation                                                |     |

| 9.2 Power Supplies in a Dual-Power-Supply System                              |     |

| 9.3 Dual-Power-Supply-Type Input/Output Buffers                               |     |

| 9.3.1 LV <sub>DD</sub> -System Input/Output Buffers                           |     |

| 9.3.1.1 LV <sub>DD</sub> -System Input Buffers                                |     |

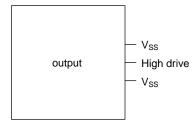

| 9.3.1.2 LV <sub>DD</sub> -System Output Buffers                               |     |

| 9.3.2 LV <sub>DD</sub> -System Fail-Safe Cells                                |     |

| 9.3.3 HV <sub>DD</sub> -System Input/Output Buffers                           |     |

| 9.3.3.1 HV <sub>DD</sub> -System Input Buffers                                |     |

| 9.3.3.2 HV <sub>DD</sub> -System Output Buffers                               | 111 |

| 9.3.3.3 HV <sub>DD</sub> -System Bidirectional Buffers                        |     |

| 9.3.4 HV <sub>DD</sub> -System Fail-Safe Cells                                |     |

| 9.4 Calculating the Delay Time in a Dual-Power-Supply System                  |     |

| 9.5 Notes on Calculating Power Consumption in a Dual-Power-Supply System      |     |

| 9.6 Estimating the Number of Power-Supply Pins in a Dual-Power-Supply System. | 121 |

| Appendix Release Note                                                         | 123 |

# **Chapter 1 Overview**

Seiko Epson's S1K50000 series consists of high-function, high-integrated CMOS standard cells based on the 0.35-micron process.

# 1.1 Features

High degree of integration

Maximum of 1,456,000 gates (2-input NAND gate equivalents)

• Operating speed Internal gate: 136 ps (3.3 V typ.), 224 ps (2.0 V typ.)

(2-input POWER NAND, standard wiring load)

Input buffer: 380 ps (5.0 V typ.) using a level shifter,

400 ps (3.3 V typ.), 1.30 ns (2.0 V typ.)

(standard wiring load)

Output buffer: 2.12 ns (5.0 V typ.) using a level shifter,

2.02 ns (3.3 V typ.), 3.90 ns (2.0 V typ.) (CL = 15 pF)

Process

CMOS 0.35-µm Al 3/4-layer metalization

• I/F level Input/output TTL-, CMOS-, and LVTTL-compatible

Input mode

TTL, CMOS, LVTTL, TTL Schmitt, CMOS Schmitt, LVTTL Schmitt, and

PCI

Internal pull-up and pull-down resistors available (two resistance val-

ues each)

Output mode Normal, tri-state, bidirectional, or PCI

Drive output I<sub>OL</sub> = 0.1 mA, 1 mA, 3 mA, 8 mA, 12 mA, or 24 mA selectable (when a

5.0-V level shifter is used)

$I_{OL} = 0.1$  mA, 1 mA, 2 mA, 6 mA, or 12 mA selectable (at 3.3 V)  $I_{OL} = 0.05$  mA, 0.3 mA, 0.6 mA, 2 mA, or 4 mA selectable (at 2.0 V)

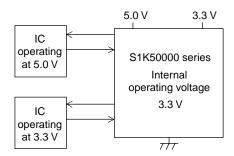

• Supports dual-power-supply operation using an internal level shifter

(Internal logic: low-voltage operation; input/output buffers: high- and

low-voltage interfaces usable in combination)

Capable of operating with V<sub>DD</sub> = 2.0 V ± 0.2 V

# 1.2 Electrical Characteristics

Table 1-1 Absolute Maximum Ratings (for a Single Power Supply)

| Parameter              | Symbol           | Rated Value                     | Unit |

|------------------------|------------------|---------------------------------|------|

| Power-Supply Voltage   | V <sub>DD</sub>  | -0.3 to 4.0                     | V    |

| Input Voltage          | VI               | -0.3 to V <sub>DD</sub> + 0.5*1 | V    |

| Output Voltage         | Vo               | -0.3 to V <sub>DD</sub> + 0.5*1 | V    |

| Output Current per Pin | lout             | ± 30                            | mA   |

| Storage Temperature    | T <sub>STG</sub> | -65 to 150                      | °C   |

<sup>\*1:</sup> This applies to N-channel open-drain, bidirectional buffers, as well as XIDC and XIDH input buffers. For Fail-Safe cells, a value in the range from -0.3 V to 7.0 V is acceptable.

Table 1-2 Absolute Maximum Ratings (for Dual Power Supplies)

| Parameter              | meter Symbol Rated Value |                                  | Unit |

|------------------------|--------------------------|----------------------------------|------|

| Dower Supply Voltage   | HV <sub>DD</sub> *3      | -0.3 to 7.0                      | V    |

| Power-Supply Voltage   | LV <sub>DD</sub> *3      | -0.3 to 4.0                      | V    |

| Innut Voltage          | HVI                      | -0.3 to HV <sub>DD</sub> + 0.5*1 | V    |

| Input Voltage          | LVI                      | -0.3 to LV <sub>DD</sub> + 0.5*1 | V    |

| Output Valtage         | HVo                      | -0.3 to HV <sub>DD</sub> + 0.5*1 | V    |

| Output Voltage         | LVo                      | -0.3 to LV <sub>DD</sub> + 0.5*1 | V    |

| Output Current per Pin | lout                     | ± 30 ( ± 50*2)                   | mA   |

| Storage Temperature    | T <sub>STG</sub>         | -65 to 150                       | °C   |

<sup>\*1:</sup> This applies to N-channel open-drain bidirectional buffers, as well as XLIDC and XLIDH or XHIDC and XHIDH input buffers. For Fail-Safe cells, a value in the range from -0.3 V to 7.0 V is acceptable.

<sup>\*2:</sup> This applies to buffers with an output current of 24 mA.

<sup>\*3:</sup>  $HV_{DD} \ge LV_{DD}$

Table 1-3-1 Recommended Operating Conditions (for a Single Power Supply)

| Parameter                  | Symbol          | Min.            | Тур.     | Max.               | Unit |

|----------------------------|-----------------|-----------------|----------|--------------------|------|

| Power-Supply Voltage       | $V_{DD}$        | 3.00            | 3.30     | 3.60               | V    |

| Input Voltage              | Vı              | V <sub>SS</sub> | _        | V <sub>DD</sub> *1 | V    |

| Ambient Temperature        | Та              | 0<br>-40        | 25<br>25 | 70*²<br>85*³       | °C   |

| Normal Input Rising Time   | t <sub>ri</sub> | _               | _        | 50                 | ns   |

| Normal Input Falling Time  | t <sub>fa</sub> | _               | _        | 50                 | ns   |

| Schmitt Input Rising Time  | t <sub>ri</sub> | _               | _        | 5                  | ms   |

| Schmitt Input Falling Time | t <sub>fa</sub> | _               | _        | 5                  | ms   |

<sup>\*1:</sup> This applies to N-channel open-drain bidirectional buffers, as well as XIDC and XIDH input buffers. For Fail-Safe cells, a value of 5.25 V or 5.50 V is acceptable.

Table 1-3-2 Recommended Operating Conditions (for a Single Power Supply)

| Parameter                  | Symbol          | Min.            | Тур.     | Max.               | Unit |

|----------------------------|-----------------|-----------------|----------|--------------------|------|

| Power-Supply Voltage       | $V_{DD}$        | 1.80            | 2.00     | 2.20               | V    |

| Input Voltage              | VI              | V <sub>SS</sub> | _        | V <sub>DD</sub> *1 | V    |

| Ambient Temperature        | Та              | 0<br>-40        | 25<br>25 | 70*2<br>85*3       | °C   |

| Normal Input Rising Time   | t <sub>ri</sub> | _               | _        | 100                | ns   |

| Normal Input Falling Time  | t <sub>fa</sub> | _               | _        | 100                | ns   |

| Schmitt Input Rising Time  | t <sub>ri</sub> | _               | _        | 10                 | ms   |

| Schmitt Input Falling Time | t <sub>fa</sub> | _               | _        | 10                 | ms   |

<sup>\*1:</sup> This applies to N-channel open-drain bidirectional buffers, as well as XIDC and XIDH input buffers. For Fail-Safe cells, a value of 5.25 V or 5.50 V is acceptable.

<sup>\*2:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = 0 to 85 [°C].

<sup>\*3:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = -40 to 125 [°C].

<sup>\*2:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = 0 to 85 [°C].

<sup>\*3:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = -40 to 125 [°C].

Table 1-4-1 Recommended Operating Conditions (for Dual Power Supplies)

| Parameter                           | Symbol           | Min.            | Тур.         | Max.                                 | Unit |

|-------------------------------------|------------------|-----------------|--------------|--------------------------------------|------|

| Power-Supply Voltage (High Voltage) | HV <sub>DD</sub> | 4.75<br>4.50    | 5.00<br>5.00 | 5.25<br>5.50                         | V    |

| Power-Supply Voltage (Low Voltage)  | LV <sub>DD</sub> | 3.00            | 3.30         | 3.60                                 | V    |

| Innut Valtage                       | HVI              | V <sub>SS</sub> | _            | HV <sub>DD</sub>                     | V    |

| Input Voltage                       | LVI              | V <sub>SS</sub> | _            | LV <sub>DD</sub> *1                  | V    |

| Ambient Temperature                 | Та               | 0<br>-40        | 25<br>25     | 70* <sup>2</sup><br>85* <sup>3</sup> | °C   |

| Normal Input Rising Time            | t <sub>ri</sub>  | _               | _            | 50                                   | ns   |

| Normal Input Falling Time           | t <sub>fa</sub>  | _               | _            | 50                                   | ns   |

| Schmitt Input Rising Time           | t <sub>ri</sub>  | _               | _            | 5                                    | ms   |

| Schmitt Input Falling Time          | t <sub>fa</sub>  | _               | _            | 5                                    | ms   |

<sup>\*1:</sup> This applies to N-channel open-drain bidirectional buffers, as well as XLIDC and XLIDH input buffers. For Fail-Safe cells, a value of 5.25 V or 5.50 V is acceptable.

Table 1-4-2 Recommended Operating Conditions (for Dual Power Supplies)

| Parameter                           | Symbol           | Min.            | Тур.     | Max.                | Unit |  |

|-------------------------------------|------------------|-----------------|----------|---------------------|------|--|

| Power-Supply Voltage (High Voltage) | HV <sub>DD</sub> | 3.00            | 3.30     | 3.60                | V    |  |

| Power-Supply Voltage (Low Voltage)  | LV <sub>DD</sub> | 1.80            | 2.00     | 2.20                | V    |  |

| Input Voltage                       | HVI              | V <sub>SS</sub> | _        | HV <sub>DD</sub> *1 | V    |  |

| Input Voltage                       | LVI              | V <sub>SS</sub> | _        | LV <sub>DD</sub> *1 | V    |  |

| Ambient Temperature                 | Та               | 0<br>-40        | 25<br>25 | 70*²<br>85*³        | ů    |  |

| Normal Input Diging Time            | Ht <sub>ri</sub> | _               | _        | 50                  | ns   |  |

| Normal Input Rising Time            | Lt <sub>ri</sub> | _               | _        | 100                 |      |  |

| Normal Input Falling Time           | Ht <sub>fa</sub> | _               | _        | 50                  | 20   |  |

| Normal Input Falling Time           | Lt <sub>fa</sub> | _               | _        | 100                 | ns   |  |

| Schmitt Input Rising Time           | Ht <sub>ri</sub> | _               | _        | 5                   | 22   |  |

| Schillitt input Kising Time         | Lt <sub>ri</sub> | _               | _        | 10                  | ms   |  |

| Schmitt Input Falling Time          | Ht <sub>fa</sub> | _               | _        | 5                   | ms   |  |

| Schillic input railing time         | Lt <sub>fa</sub> | _               | _        | 10                  | 1115 |  |

<sup>\*1:</sup> This applies to N-channel open-drain bidirectional buffers, as well as XLIDC and XLIDH or XHIDC and XHIDH input buffers. For Fail-Safe cells, a value of 5.25 V or 5.50 V is acceptable.

<sup>\*2:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = 0 to 85 [°C].

<sup>\*3:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = -40 to 125 [°C].

<sup>\*2:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = 0 to 85 [°C].

<sup>\*3:</sup> This temperature range refers to the recommended ambient temperature in cases where Tj = -40 to 125 [°C].

Table 1-5 Electrical Characteristics

(HV<sub>DD</sub> = 5 V common;  $V_{SS}$  = 0 V; Ta = -40°C to 85°C)

| Symbol                                            | Test Con                                                                                                                                      | ditions | Min.                     | Тур. | Max.         | Unit     |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------|------|--------------|----------|

| ILI                                               | _                                                                                                                                             | •       | -1                       | _    | 1            | μA       |

| loz                                               | _                                                                                                                                             |         | -1                       | _    | 1            | μA       |

| V <sub>OH</sub>                                   | I <sub>OH</sub> = -0.1 mA (Type S), -1 mA (Type M) -3 mA (Type 1), -8 mA (Type 2) -12 mA (Type 3, Type 4) HV <sub>DD</sub> = Min.             |         | HV <sub>DD</sub><br>-0.4 | _    | _            | V        |

| V <sub>OL</sub>                                   | I <sub>OL</sub> = 0.1 mA (Type S), 1 mA (Type M)<br>3 mA (Type 1), 8 mA (Type 2)<br>12 mA (Type 3), 24 mA (Type 4)<br>HV <sub>DD</sub> = Min. |         | _                        |      | 0.4          | V        |

| V <sub>IH1</sub>                                  | CMOS level, HV <sub>DD</sub>                                                                                                                  | = Max.  | 3.5                      | 1    | _            | V        |

| V <sub>IL1</sub>                                  | CMOS level, HV <sub>DD</sub>                                                                                                                  | = Min.  | _                        |      | 1.0          | V        |

| V <sub>T1+</sub>                                  | CMOS Schmitt                                                                                                                                  |         | 2.0                      |      | 4.0          | V        |

| V <sub>T1-</sub>                                  | CMOS Schmitt                                                                                                                                  |         | 0.8                      |      | 3.1          | V        |

| V <sub>H1</sub>                                   | CMOS Schmitt                                                                                                                                  |         | 0.3                      | _    | _            | V        |

| V <sub>IH2</sub>                                  | TTL level, HV <sub>DD</sub> = I                                                                                                               | Max.    | 2.0                      | _    | _            | V        |

| V <sub>IL2</sub>                                  | TTL level, HV <sub>DD</sub> = I                                                                                                               | Min.    | _                        |      | 0.8          | V        |

| V <sub>T2+</sub>                                  | TTL Schmitt                                                                                                                                   |         | 1.2                      |      | 2.4          | V        |

| V <sub>T2</sub> -                                 | TTL Schmitt                                                                                                                                   |         | 0.6                      |      | 1.8          | V        |

| V <sub>H2</sub>                                   | TTL Schmitt                                                                                                                                   |         | 0.1                      | _    | _            | V        |

| V <sub>IH3</sub>                                  | PCI level, HV <sub>DD</sub> = I                                                                                                               | Мах.    | 2.0                      |      | _            | V        |

| V <sub>IL3</sub>                                  | PCI level, HV <sub>DD</sub> = I                                                                                                               | Min.    | _                        | _    | 0.8          | V        |

| I <sub>OH3</sub>                                  | For PCI, V <sub>OH</sub> = 1.4 V, HV <sub>DD</sub> = Min.<br>V <sub>OH</sub> = 3.1 V, HV <sub>DD</sub> = Max.                                 |         | -44<br>—                 |      | <br>-142     | mA<br>mA |

| I <sub>OL3</sub>                                  | For PCI, $V_{OL} = 2.20 \text{ V}$ , $HV_{DD} = \text{Min}$ .<br>$V_{OL} = 0.71 \text{ V}$ , $HV_{DD} = \text{Max}$ .                         |         | 95<br>—                  |      | <br>206      | mA<br>mA |

| R <sub>PU</sub>                                   | V <sub>I</sub> = 0 V                                                                                                                          | Type 1  | 30                       | 60   | (120)<br>144 | kΩ       |

|                                                   | V1 = 0 V                                                                                                                                      | Type 2  | 60                       | 120  | (240)<br>288 |          |

| n Resistance*1 R <sub>PD</sub> V <sub>I</sub> = V | V. = Vop                                                                                                                                      | Type 1  | 30                       | 60   | (120)<br>144 | kΩ       |

| NPD                                               | VI - VDD                                                                                                                                      | Type 2  | 60                       | 120  | (240)<br>288 | K32      |

| I <sub>BHH</sub>                                  |                                                                                                                                               |         | _                        | -    | -80          | μΑ       |

| I <sub>BHL</sub>                                  |                                                                                                                                               |         | _                        | _    | 33           | μΑ       |

| I <sub>BHHO</sub>                                 | For bus hold, $V_{IN} = 0.8 \text{ V}$<br>$HV_{DD} = Max.$                                                                                    |         | -550                     | _    | _            | μA       |

| I <sub>BHLO</sub>                                 | For bus hold, $V_{IN} = 2.0 \text{ V}$<br>$HV_{DD} = \text{Max}.$                                                                             |         | 330                      |      | _            | μΑ       |

| C <sub>I</sub>                                    | f = 1 MHz, HV <sub>DD</sub> =                                                                                                                 | 0 V     |                          |      | 10           | pF       |

| Co                                                | f = 1 MHz, HV <sub>DD</sub> =                                                                                                                 | 0 V     |                          |      | 10           | pF       |

| C <sub>IO</sub>                                   | f = 1 MHz, HV <sub>DD</sub> =                                                                                                                 | 0 V     |                          | 1    | 10           | pF       |

|                                                   | ILI   IOZ     VOH                                                                                                                             | ILI     | ILI                      | I_L  | ILI          | ILI      |

<sup>\*1:</sup> The values in ( ) apply to cases where Ta = 0°C to 70°C.

<sup>\*2:</sup> Conforms to PCI standard Rev. 2.2

Table 1-6 Electrical Characteristics

$(V_{DD} = LV_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{Vss} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                       | Symbol            | Test Cor                                                                                                            | nditions                                                                                                                          | Min.     | Тур. | Max.         | Unit |

|---------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|------|--------------|------|

| Quiescent Current*1             | I <sub>DDS</sub>  | Static state                                                                                                        |                                                                                                                                   | _        | _    | 170          | μΑ   |

| Input Leakage Current           | ILI               | _                                                                                                                   |                                                                                                                                   | -1       | _    | 1            | μΑ   |

| Off-State Leakage Current       | l <sub>OZ</sub>   |                                                                                                                     |                                                                                                                                   | -1       | _    | 1            | μA   |

| High-Level Output Voltage       | V <sub>ОН</sub>   | -2 mA (Type 1)                                                                                                      | I <sub>OH</sub> = -0.1 mA (Type S), -1 mA (Type M)<br>-2 mA (Type 1), -6 mA (Type 2)<br>-12 mA (Type 3)<br>V <sub>DD</sub> = Min. |          | _    | _            | ٧    |

| Low-Level Output Voltage        | V <sub>OL</sub>   | 2 mA (Type 1),                                                                                                      | I <sub>OL</sub> = 0.1 mA (Type S), 1 mA (Type M)<br>2 mA (Type 1), 6 mA (Type 2)<br>12 mA (Type 3)<br>V <sub>DD</sub> = Min.      |          | _    | 0.4          | ٧    |

| High-Level Input Voltage        | V <sub>IH1</sub>  | LVTTL level, V <sub>DD</sub> =                                                                                      | Max.                                                                                                                              | 2.0      | _    | _            | V    |

| Low-Level Input Voltage         | V <sub>IL1</sub>  | LVTTL level, V <sub>DD</sub> =                                                                                      | Min.                                                                                                                              | _        | _    | 0.8          | V    |

| Positive Trigger Voltage        | V <sub>T1+</sub>  | LVTTL Schmitt                                                                                                       |                                                                                                                                   | 1.1      | _    | 2.4          | V    |

| Negative Trigger Voltage        | V <sub>T1-</sub>  | LVTTL Schmitt                                                                                                       |                                                                                                                                   | 0.6      |      | 1.8          | V    |

| Hysteresis Voltage              | V <sub>H1</sub>   | LVTTL Schmitt                                                                                                       |                                                                                                                                   | 0.1      |      | _            | V    |

| High-Level Input Voltage*3      | V <sub>IH3</sub>  | PCI level, V <sub>DD</sub> = Max.                                                                                   |                                                                                                                                   | 1.71     | _    | _            | V    |

| Low-Level Input Voltage*3       | V <sub>IL3</sub>  | PCI level, V <sub>DD</sub> = Min.                                                                                   |                                                                                                                                   | _        | _    | 0.98         | V    |

| High-Level Output Voltage*3     | I <sub>OH3</sub>  | For PCI, $V_{OH} = 0.90 \text{ V}$ , $V_{DD} = \text{Min}$ .<br>$V_{OH} = 2.52 \text{ V}$ , $V_{DD} = \text{Max}$ . |                                                                                                                                   | -36<br>— | _    | <br>-115     | mA   |

| Low-Level Output Voltage*3      | I <sub>OL3</sub>  | For PCI, $V_{OL} = 1.80 \text{ V}$ , $V_{DD} = \text{Min}$ .<br>$V_{OL} = 0.65 \text{ V}$ , $V_{DD} = \text{Max}$ . |                                                                                                                                   | 48<br>—  |      | —<br>137     | mA   |

| Pull Un Popietonos*?            | R <sub>PU</sub>   | V <sub>I</sub> = 0 V                                                                                                | Type 1                                                                                                                            | 20       | 50   | (100)<br>120 | kΩ   |

| Pull-Up Resistance*2            | KPU               | V   = 0 V                                                                                                           | Type 2                                                                                                                            | 40       | 100  | (200)<br>240 | K52  |

| Pull-Down Resistance*2          | R <sub>PD</sub>   | $V_I = V_{DD}$                                                                                                      | Type 1                                                                                                                            | 20       | 50   | (100)<br>120 | kΩ   |

| T un bown resistance            | NPD               | V1 - VDD                                                                                                            | Type 2                                                                                                                            | 40       | 100  | (200)<br>240 | 1/22 |

| High-Level Hold Current         | I <sub>BHH</sub>  | For bus hold, $V_{IN} = V_{DD}$ =                                                                                   | 2.0 V<br>= Min.                                                                                                                   | _        | _    | -20          | μΑ   |

| Low-Level Hold Current          | I <sub>BHL</sub>  | For bus hold, $V_{IN} = V_{DD}$                                                                                     | 0.8 V<br>= Min.                                                                                                                   | _        | _    | 17           | μА   |

| High-Level Reversing<br>Current | I <sub>BHHO</sub> | For bus hold, $V_{IN} = 0.8 V$<br>$V_{DD} = Max$ .                                                                  |                                                                                                                                   | -350     | _    | _            | μΑ   |

| Low-Level Reversing<br>Current  | I <sub>BHLO</sub> | For bus hold, V <sub>IN</sub> = V <sub>DD</sub> =                                                                   | 2.0 V<br>= Max.                                                                                                                   | 210      | _    | _            | μΑ   |

| Input-Pin Capacitance           | Cı                | f = 1 MHz, V <sub>DD</sub> = 0                                                                                      | V                                                                                                                                 | _        | _    | 10           | pF   |

| Output-Pin Capacitance          | Co                | f = 1 MHz, V <sub>DD</sub> = 0                                                                                      | V                                                                                                                                 | _        | _    | 10           | pF   |

| Input/Output-Pin Capacitance    | C <sub>IO</sub>   | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                    |                                                                                                                                   | _        | _    | 10           | pF   |

<sup>\*1:</sup> The quiescent current represents the typical value for each series at Tj = 85°C. For details, see Tables 1-8 through 1-9.

<sup>\*2:</sup> The values in ( ) apply to cases where Ta = 0°C to 70°C. For cases where  $HV_{DD}$  = 3.3 V + 0.3 V;  $V_{SS}$  = 0 V; Ta = -40°C to 85°C, each value should be doubled.

<sup>\*3:</sup> Conforms to PCI standard Rev. 2.2

Table 1-7 Electrical Characteristics

$(V_{DD} = LV_{DD} = 2.0 \text{ V} \pm 0.2 \text{ V}, \text{Vss} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                       | Symbol            | Test Con                                                                                                                              | ditions         | Min.                    | Тур. | Max. | Unit  |

|---------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|------|------|-------|

| Quiescent Current*1             | I <sub>DDS</sub>  | Static state                                                                                                                          |                 | _                       | _    | 150  | μA    |

| Input Leakage Current           | ILI               | _                                                                                                                                     |                 | -1                      | _    | 1    | μA    |

| Off-State Leakage Current       | l <sub>OZ</sub>   | _                                                                                                                                     |                 | -1                      | _    | 1    | μΑ    |

| High-Level Output Voltage       | V <sub>OH</sub>   | I <sub>OH</sub> = -0.05 mA (Type S), -0.3 mA (Type M)<br>-0.6 mA (Type 1), -2 mA (Type 2)<br>-4 mA (Type 3)<br>V <sub>DD</sub> = Min. |                 | V <sub>DD</sub><br>-0.2 | _    | _    | V     |

| Low-Level Output Voltage        | V <sub>OL</sub>   | I <sub>OL</sub> = 0.05 mA (Type S), 0.3 mA (Type M)<br>0.6 mA (Type 1), 2 mA (Type 2)<br>4 mA (Type 3)<br>V <sub>DD</sub> = Min.      |                 | _                       | _    | 0.2  | V     |

| High-Level Input Voltage        | V <sub>IH1</sub>  | CMOS level, V <sub>DD</sub> =                                                                                                         | : Max.          | 1.6                     | _    | _    | V     |

| Low-Level Input Voltage         | V <sub>IL1</sub>  | CMOS level, V <sub>DD</sub> = Min.                                                                                                    |                 | _                       | _    | 0.3  | V     |

| Positive Trigger Voltage        | V <sub>T1+</sub>  | CMOS Schmitt                                                                                                                          |                 | 0.4                     | _    | 1.6  | V     |

| Negative Trigger Voltage        | V <sub>T1-</sub>  | CMOS Schmitt                                                                                                                          |                 | 0.3                     | _    | 1.4  | V     |

| Hysteresis Voltage              | V <sub>H1</sub>   | CMOS Schmitt                                                                                                                          |                 | 0                       | _    | _    | V     |

| Pull-Up Resistance              | R <sub>PU</sub>   | V <sub>I</sub> = 0 V                                                                                                                  | Type 1          | 30                      | 120  | 300  | kΩ    |

| Full-Op Resistance              | TYPU              | V  = 0 V                                                                                                                              | Type 2          | 60                      | 240  | 600  | N22   |

| Pull-Down Resistance            | R <sub>PD</sub>   | $V_{I} = V_{DD}$                                                                                                                      | Type 1          | 30                      | 120  | 300  | kΩ    |

| T ull Bowii Resistance          | TYPU              | VI = VDD                                                                                                                              | Type 2          | 60                      | 240  | 600  | 11.32 |

| High-Level Hold Current         | I <sub>BHH</sub>  | For bus hold, V <sub>IN</sub> = V <sub>DD</sub> =                                                                                     | 1.6 V<br>= Min. | _                       | _    | -2   | μА    |

| Low-Level Hold Current          | I <sub>BHL</sub>  | For bus hold, $V_{IN} = 0.3 \text{ V}$<br>$V_{DD} = \text{Min}.$                                                                      |                 | _                       | _    | 2    | μА    |

| High-Level Reversing<br>Current | I <sub>BHHO</sub> | For bus hold, $V_{IN} = 0.3 \text{ V}$<br>$V_{DD} = \text{Max}.$                                                                      |                 | -100                    | _    | _    | μА    |

| Low-Level Reversing<br>Current  | I <sub>BHLO</sub> | For bus hold, $V_{IN} = 1.6 \text{ V}$<br>$V_{DD} = \text{Max}$ .                                                                     |                 | 100                     | _    | _    | μА    |

| Input-Pin Capacitance           | Cı                | f = 1 MHz, V <sub>DD</sub> = 0                                                                                                        | V               | _                       | _    | 10   | pF    |

| Output-Pin Capacitance          | Co                | f = 1 MHz, V <sub>DD</sub> = 0                                                                                                        | V               | _                       | _    | 10   | pF    |

| Input/Output-Pin<br>Capacitance | C <sub>IO</sub>   | f = 1 MHz, V <sub>DD</sub> = 0 V                                                                                                      |                 | _                       | _    | 10   | pF    |

<sup>\*1:</sup> The quiescent current represents the typical value for each series at Tj = 85°C. For details, see Tables 1-8 through 1-9.

Table 1-8 Quiescent Current (for a Single Power Supply)

$(Ti = 85^{\circ}C)$

| Parameter           | 3.3 V ± 0.3 V<br>I <sub>DDS</sub> Max. | 2.0 V ± 0.2 V<br>I <sub>DDS</sub> Max. | Unit |

|---------------------|----------------------------------------|----------------------------------------|------|

| Quiescent Current*1 | 35 to 260                              | 31 to 230                              | μΑ   |

<sup>\*1:</sup> Varies with the chip size and incorporated macro

Table 1-9 Quiescent Current (for Dual Power Supplies)

$(Tj = 85^{\circ}C)$

| Parameter           | 5 V ± 10%<br>HI <sub>DDS</sub> Max. | 3.3 V ± 0.3 V<br>LI <sub>DDS</sub> Max. | 3.3 V ± 0.3 V<br>HI <sub>DDS</sub> Max. | 2.0 V ± 0.2 V<br>LI <sub>DDS</sub> Max. | Unit |

|---------------------|-------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|------|

| Quiescent Current*1 | 30 to 80                            | 35 to 260                               | 25 to 60                                | 31 to 230                               | μΑ   |

HI<sub>DDS</sub>: Quiescent current between HV<sub>DD</sub> and V<sub>SS</sub>; LI<sub>DDS</sub>: Quiescent current between LV<sub>DD</sub> and V<sub>SS</sub>

For the quiescent current in cases where  $Tj = 85^{\circ}C$ , an approximate value can be obtained using the equation below ( $Tj = -40^{\circ}C$  to  $85^{\circ}C$ , however).

$$I_{DD}$$

(Tj) =  $I_{DDS}$  (Tj = 85°C) × temperature coefficient

=  $I_{DDS}$  (Tj = 85°C) × 10 $\frac{T_{J-85}}{60}$

(For cases where  $T_i = 125$ °C, calculate the above using temperature coefficient = 12.)

For dual power supplies, the sum of quiescent currents for the respective voltages used comprises a total quiescent current. (HI<sub>DDS</sub> + LI<sub>DDS</sub>)

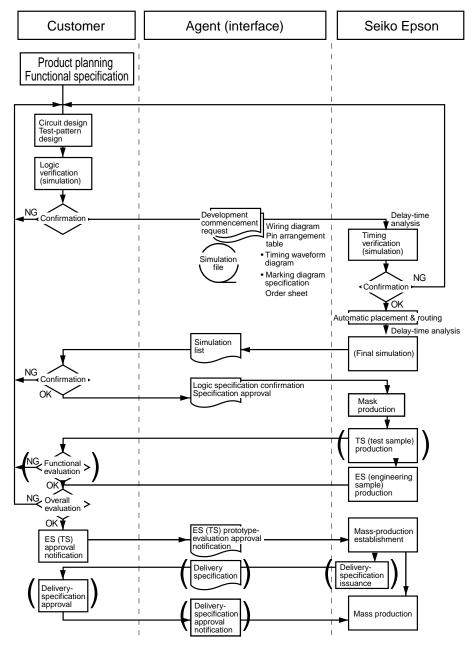

# 1.3 Outline of Standard-Cell Development Flow

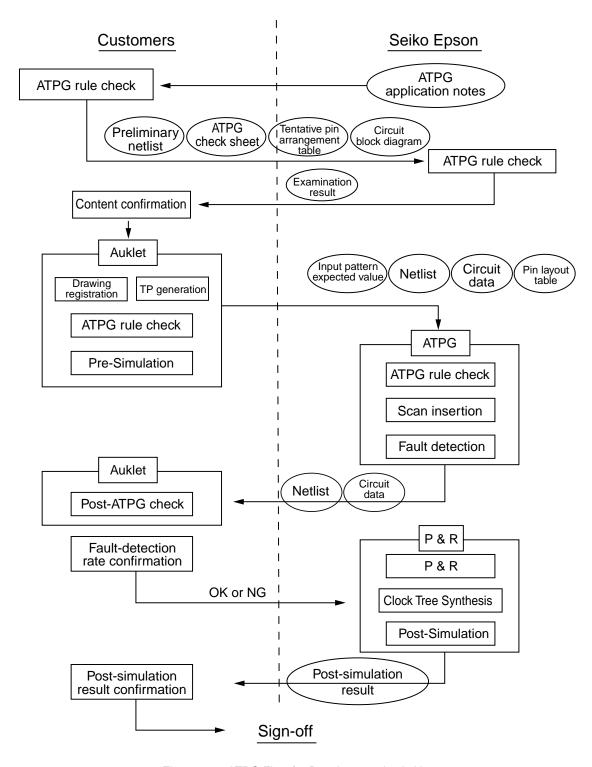

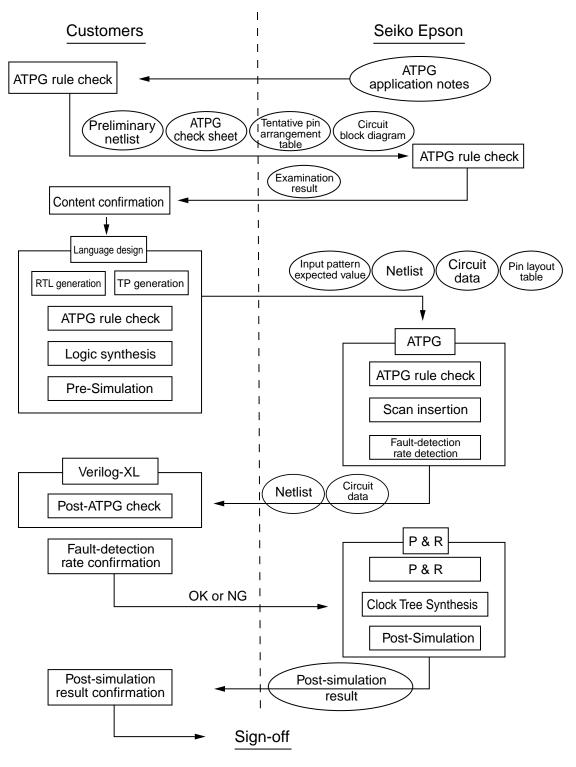

The standard cells were developed through collaboration between Seiko Epson and its customers. Customers perform a range of work, from system and circuit designs to test-pattern design, using the cell libraries and various design materials offered by Seiko Epson.

For interfacing information, customers are expected to conduct preliminary checks based on the data-release checklist included in the appendix herein, and present the necessary data and documentation to Seiko Epson.

Customers are responsible for conducting simulations using the EDA software or Auklet\* on hand; the remainder of the work, beginning with placement and routing, is undertaken by Seiko Epson.

Note) \*1 : Auklet is Seiko Epson's ASIC design support system and can be run on MS Windows 95/98/NT.

The following EDA software can currently be simulated:

- Verilog-XL (\*1)

- VSS (\*2)

- ModelSim (\*3)

Note) \*1 : Verilog-XL is a registered trademark of Cadence Design Systems of the U.S.

Note) \*2: VSS is a registered trademark of Synopsys of the U.S.

Note) \*3 : ModelSim is a registered trademark of Model Technology of the U.S.

For details, please contact Seiko Epson or its distributor.

<sup>\*1:</sup> Varies with the chip size and incorporated macro

The diagram below shows the flow of the standard cell development procedure.

Those tasks enclosed in ( ) are undertaken when requested by the customer.

# **Chapter 2 Precautions on Circuit Design**

# 2.1 Insertion of Input/Output Buffers

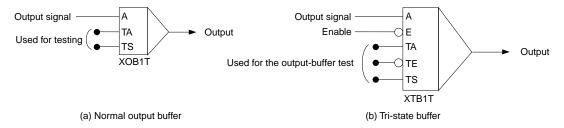

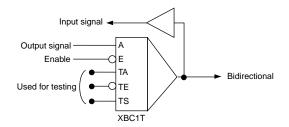

In the design of your circuit, always be sure to use input/output buffers to exchange signals with external devices. Because CMOS ICs are extremely susceptible to damage by static electricity, the input/output buffers contain protective circuits.

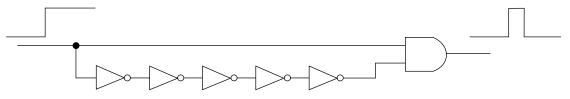

# 2.2 Use of Differentiating Circuits Inhibited

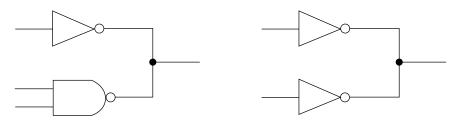

In LSIs, the tpd of each gate varies depending on the process dispersions during mass production or the operating environment. Therefore, differentiating circuits using the relative time difference of tpd like the one shown in Figure 2-1 cannot obtain a sufficient pulse width, causing the circuit to operate erratically.

When it is necessary to use a differentiating circuit, be sure to use one that utilizes flip-flops, rather than the one shown in Figure 2-1.

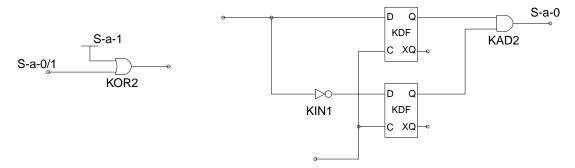

Figure 2-1 Example of a Differentiating Circuit

# 2.3 Wired Logic Inhibited

Because CMOS transistors are used, wired logic cannot be configured as in bipolar transistors. Therefore, the output pins of cells cannot be connected together, as shown in Figure 2-2. Output pins can only be connected together in a bus-circuit configuration.

Figure 2-2 Example of Inhibited Wired Logic

# 2.4 Hazard Protection

In circuits or decoders configured by combining gates such as NAND or NOR gates, a very short pulse may be generated due to the difference in delay times between gates. This short pulse is known as a hazard, and it causes malfunction when fed into the clock or reset pins of flip-flips.

Therefore, circuits where such a hazard is likely to occur must be configured so as to prevent the hazard from propagating. For decoders, it may be necessary to use a circuit that has an enable pin.

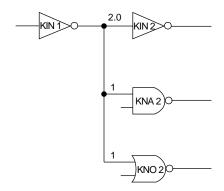

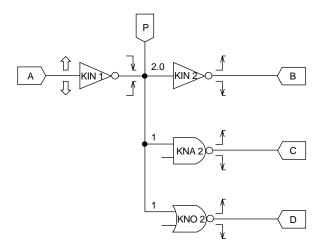

# 2.5 Fan-Out Limitations

The tpd of logic gates is determined by the load capacitance of their output pin. An excessively large load capacitance may not only cause the tpd to become large, but may also cause malfunction. Therefore, there are limitations on the number of loads that can be connected to the output pins of each logic gate. These are known as "fan-out" limitations.

The input-pin capacitance of each logic gate, however, tends to differ depending on the logic-gate input. The input capacitance of each logic gate, in terms of the input capacitance of an inverter (KINI) = 1, is known as "fan-in."

In the design of your circuit, make sure the total number of fan-ins connected to the output pins of each logic gate does not exceed the fan-out limitations of those output pins.

Furthermore, for logic gates operating at high speed, such as high-speed clock lines (fmax = 40 MHz or more), make sure the output-pin capacitance of those gates is approximately half the fan-out limitation.

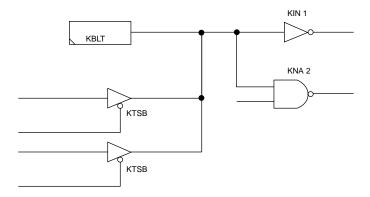

# 2.6 Internal Bus Circuits

A bus circuit is configured with 3-state logic circuits, so one of the outputs connected to the bus can be driven active (while the other outputs are placed in the high-impedance state) by turning the bus control signals on or off.

In this way, a transmission-signal line on the bus is shared by dividing it in time. Although bus circuits are very effective for logic design, note the following when using a bus circuit.

#### Precautions on the use of bus circuits

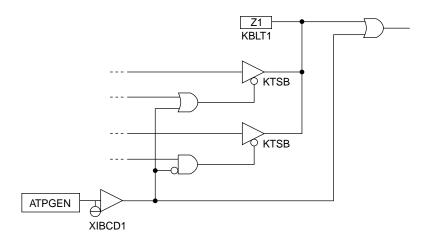

- (1) Bus cells can only be used for bus circuits (for the S1K50000-series bus cells, see Table 2-1).

- (2) When using bus cells, add bus definition cells KBLT to the bus in the configuration of your circuit.

- (3) Up to 32 bus cells can be connected to one length of bus.

- (4) Of the bus cells connected to one length of bus, only one output can be active (0 or 1) at one time, and all other bus cell outputs must be placed in the high-impedance state (Z).

- (5) Even when all of the bus cells connected to one length of bus are in the high-impedance state (Z), data may be retained by a bus latch cell. However, the retained data should be left floating, and should not be used as logic signals.

- (6) In the creation of your test pattern, make sure the bus' initial state will settle easily, to ensure improved testability. In addition, add one or more test pins to make the bus easily controllable.

- (7) The bus control signals within the same event rate can be switched only once.

- (8) Excessive fan-out of the bus circuit may cause the propagation delay time to increase, making high-speed operation difficult.

The usable bus cells in the S1K50000 series are listed in Table 2-1.

Table 2-1 S1K50000-Series Bus Cells

| Cell Type                                         | Cell Name                    |        |        |  |  |

|---------------------------------------------------|------------------------------|--------|--------|--|--|

| Cell Type                                         | 1 BIT                        | 4 BIT  | 8 BIT  |  |  |

| Bus latches                                       | KBLT 1                       | KBLT 4 | KBLT 8 |  |  |

| Bus driver                                        | KTSB, KTSB4, KTSB8,<br>KTSBP | KT244H | KT244  |  |  |

| Inverting bus driver                              | KTSV, KTSV4, KTSV8,<br>KTSVP | KT240H | KT240  |  |  |

| Transparent latches with reset and 3-state output | _                            | KT373H | KT373  |  |  |

| D-flip flops with rest and 3-state output         | _                            | KT374H | KT374  |  |  |

| 1-bit RAM                                         | KRM1                         | _      | _      |  |  |

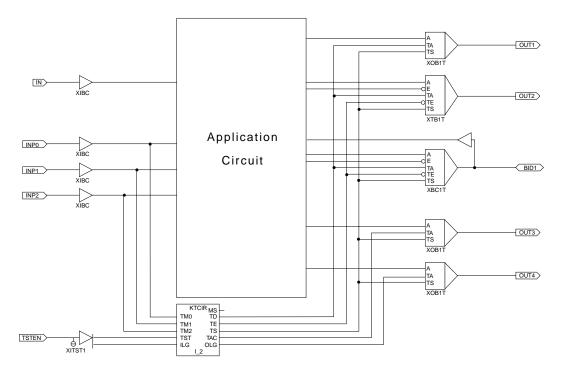

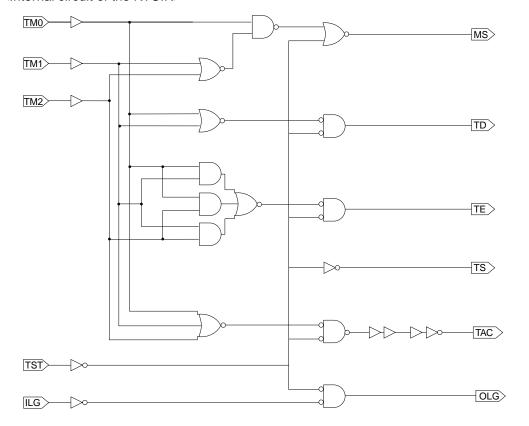

Figure 2-3 Typical Configuration of a Bus Cell Circuit

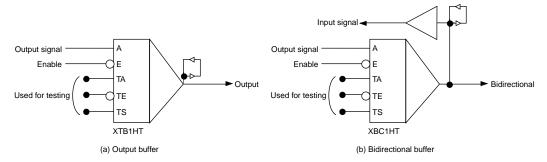

# 2.7 Bus Hold Circuits

Available with the S1K50000 series are input/output buffers with a bus hold function to hold the input/output-pin data in order to prevent the output pins or bidirectional pins from entering a high-impedance state.

However, because the retention capability of the bus hold circuit is repressed so as not to adversely affect normal bus operation, do not use the retained output as valid data. If any data is fed from an external device, the state of the data may change easily.

For details on the bus hold circuit's output retention current, see Tables 1-5 through 1-7.

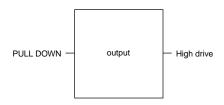

Figure 2-4 Typical Bus Hold Circuit Symbol

# 2.8 Precautions on Creating Circuit Diagrams (Logic Diagrams)

For diagram interfaces, circuit diagrams are normlly presented to Seiko Epson by the customer. In the creation of your circuit diagrams, note the following:

- For the Seiko Epson format, use the logic symbols listed in "Standard Cell S1K50000-Series MSI Cell Library."

- Do not use the aslant wiring shown in the circuit diagram.

- To write input/output and bidirectional pin names, use 2 to 32 alphanumeric characters beginning with an English letter.

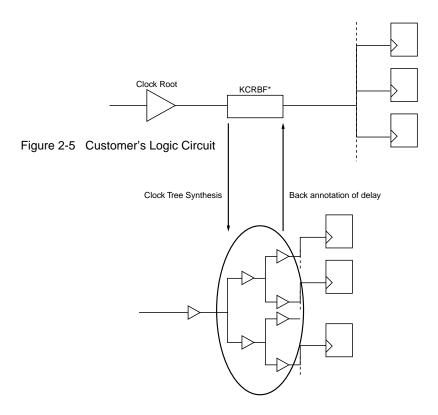

# 2.9 Clock Tree Synthesis

# (1) Outline

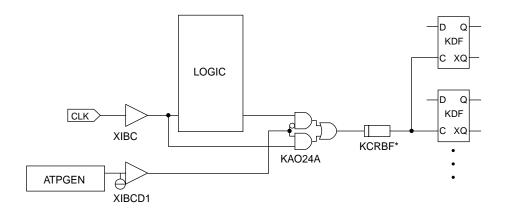

Clock Tree Synthesis is a service that automatically inserts a tree of a set of buffers with optimized clock line skew and delay. In some cases, clock trees are inserted by the customers themselves for the purpose of clock line fan-out adjustment or the like. However, because in such a case trees are automatically placed and routed by P&R tools, the clock line may, in effect, have an increased clock skew. In addition, wiring delay may eventually be increased to a greater extent than predicted, as placement & routing and cell delays are often imbalanced. Clock Tree Synthesis solves all of these problems efficiently.

#### (2) Method of practice

Before a clock tree can be automatically inserted, the clock line must have a dedicated buffer inserted by the customer for the following three purposes:

- · Determination of the location at which to apply Clock Tree Synthesis

- Performance of a preliminary routing-level simulation (pre-simulation) through estimation of the delay in the inserted clock tree

- Back annotation of the delay in the inserted clock tree to allow the performance of precise post-simulation

Choose the dedicated buffer for Clock Tree Synthesis from the table of dedicated buffers provided later. When inserting the selected dedicated buffer, handle it the same way as with ordinary cells by referring to the "image diagram," in consideration of the "restrictions and precautions." In addition, for logic-synthesis-based design, because the dedicated buffer cannot be automatically inserted, write the procedure using description language directly. At that time, execute the command specified below to ensure that another buffer will not be synthesized on the clock line in which the dedicated buffer has been inserted:

set\_dont\_touch\_net net\_name

#### [Dedicated buffers]

Choose the dedicated buffer from among those listed below, in accordance with the fan-out.

|           | S1K50000 Series |                           |

|-----------|-----------------|---------------------------|

| Cell Name | To Max. (ns)    | Approximate Fan-Out Count |

| KCRBF2    | 2.00            | 0 to 500                  |

| KCRBF3    | 3.00            | 500 to 3000               |

| KCRBF4    | 4.00            | 3000 to 10000             |

| KCRBF5    | 5.00            | Over 10000                |

| KCRBF6    | 6.00            |                           |

| KCRBF7    | 7.00            |                           |

| KCRBF8    | 8.00            |                           |

Note 1: The K value of these cells (delay due to fan-out) is set to 0 in pre-simulation.

Note 2: The fan-out counts for these cells are set to infinity.

Note 3: The delay relative to the fan-out counts is only an approximate value for use as a guideline.

#### [Restrictions and precautions]

- Applicable series: S1L9000F, S1L30000, S1L35000, S1L50000, S1K50000

- The dedicated buffers can only be used for the purpose of Clock Tree Synthesis.

- Clock Tree Synthesis can also be applied to data lines or other control signals. However, if

the number of nets to which Clock Tree Synthesis is applied increases, a large skew or delay

may result. Therefore, limit the number of synthesized nets to 10, and limit the application of

synthesis to critical nets with a large fan-out.

- The application of Clock Tree Synthesis to nets with a small fan-out may result in increased delay or skew. Apply synthesis only to nets that have a fan-out of several tens or more.

- Clock Tree Synthesis may also help to adjust the skew between multiple clock lines. In such

a case, consult Seiko Epson after presenting a detailed block diagram (clearly showing the

clock-line structure).

- For a set of clock lines that have the same clock root and are divided into multiple clock lines by gates or the like, "Gated Clock-Tree Synthesis Explanation Data" is separately required. In such a case, contact Seiko Epson.

# [Required information]

To ensure the efficient use of Clock Tree Synthesis, please send the information specified below to Seiko Epson by the time data is released.

| Instance Name of KCRBF* | Target Skew Value | Target Delay Value<br>(Min./Max.) |

|-------------------------|-------------------|-----------------------------------|

|                         |                   |                                   |

|                         |                   |                                   |

|                         |                   |                                   |

|                         |                   |                                   |

|                         |                   |                                   |

Note 1: The target values are only approximate for use as guidelines in the application of synthesis, and it is not guaranteed that the values will be satisfied.

Note 2: If you do not have definite target values, specify your desired values by entering a comment (e.g., "as small as possible").

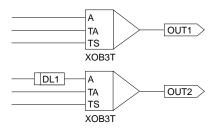

# [Image diagram]

Shown below is an example of a logic-circuit diagram to be presented by the customer and a layout-circuit diagram derived from it through the application of Clock Tree Synthesis at Seiko Epson.

Figure 2-6 Layout Diagram Derived by Applying Clock Tree Synthesis at Seiko Epson

# 2.10 ATPG (Auto Test-Pattern Generation)

# (1) Introduction

ATPG refers to automatic pattern generation, for which tools are released from each tool vendor. Testgen from Synopsys is used for ASIC design by Seiko Epson. Use of Testgen helps to automatically generate a test pattern following the insertion of scan circuits into the original circuit.

The word "control" as used in this manual means that any level can be applied to the target pin without being routed via a sequential circuit. That is, it does not refer to clocks, such as divided-by-N clocks, that require several cycles for status settings. For example, the description, "Each flip-flop can have its clock controlled from the outside" refers to a circuit in which an external input clock (clocking source) can reach each flip-flop.

#### (2) Outline

Scan insertion is executed on circuits that conform to the design rules required for ATPG support, and fault detection by ATPG is performed. In addition, because ATPG tools operate the internal nodes forcibly from external pins through a scan circuit, the test patterns output by ATPG tools cannot be used to observe operation of the user circuit. Therefore, customers are requested to create the test pattern necessary to verify the basic operation of the circuit. In other words, keep in mind that the test patterns generated by ATPG tools are used only for the purpose of increasing the fault detection rate. The use of ATPG tools helps to generate a test pattern that, for full-scan circuits, can attain a high fault detection rate of close to 100%, except for untestable nodes in which logical fault detection is impossible. Note that ATPG uses the full-scan method based on MUXSCAN-type flip-flops.

# (3) Definition of the fault detection rate

The single-degeneracy fault mode is used.

SA0: Fixed (shorted) to 0 SA1: Fixed (shorted) to 1

The ATPG tool (TestGen) generates the test pattern shown below.

A test pattern is generated in such a way that SA1 and SA0 are set for each node and that, when they are fixed to the observable logic level of 0 or 1, a functional failure results.

Figure 2-7 Example of an Untestable Fault

# (4) Design flow (1/2)

Figure 2-8 ATPG Flow for Development by Auklet

# (4) Design flow (2/2)

Figure 2-9 ATPG Flow for Development by Logic Synthesis

#### (5) Configuration of test patterns generated by ATPG

The test patterns generated by ATPG have the two modes specified below, and these two modes must be switched over using a scan enable input pin (SCANEN). Because the SCANEN pin is connected for circuit scanning, make sure your circuits have this pin prepared as a dedicated input pin.

#### · Scan shift mode

In this mode, data is input and output to and from the circuit's internal storage device (flip-flop) configured as a shift register.

#### Scan test mode

In this mode, the data applied to the storage device in scan shift mode is operated internally through the entry of a clock.

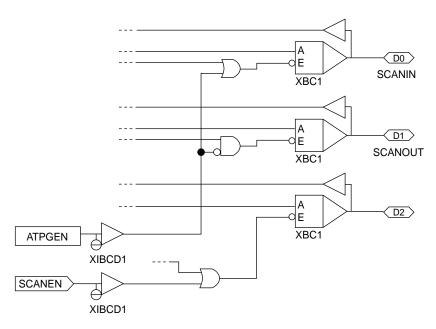

## (6) Input/output pins for ATPG

The pins needed for ATPG are described below. Of these, the provision of two pins, SCANEN and ATPGEN, is sufficient for ATPG to be run efficiently. This may result in a reduced delivery period and an increased fault detection rate, however.

# Scan enable input pin (SCANEN)

This pin is used to switch between scan-shift and scan-test modes. It also is used to reset or set the flip-flop, and to fix the bidirectional input/output select signal during scan shift. Because this pin is always necessary for scanning, be sure to prepare it as a dedicated input pin.

#### ATPG test input pin (ATPGEN)

This pin makes the circuit suitable for ATPG, and is used to fix the circuit's internal asynchronous parts or for switchover to make clock lines controllable that cannot be controlled from the outside. This pin is unnecessary if the ATPG rules were taken into consideration in the design of the original circuit. Prepare this pin as a dedicated input pin.

#### Scan data input pin

This input pin is used to set data in the shift register generated by scanning. Two or more of these pins may exist, depending on the number of scan flip-flops, and this pin may be shared with other pins. However, it cannot be shared with the control pins that reset/set the clock, nor can it be shared with other pins employed for scanning. If it is shared with bidirectional pins, make sure the pin is always in input state through the use of the ATPGEN pin, for example.

#### · Scan data output pin

This pin is used to read data from the shift register generated by scanning. Two or more of these pins may exist, depending on the number of scan flip-flops, and this pin may be shared with other pins. However, if it is shared with bidirectional pins, make sure the pin is always in output state through the use of the ATPGEN pin, for example.

Scan clock input pin

This clock input pin is in the test pattern generated by ATPG. In most cases, this pin uses the system clock during normal operation.

# (7) Logic circuit design rules for ATPG support (DFT)

In order for ATPG to be performed, the logic circuit is scanned. In the creation of the original circuit, be sure to follow the rules specified below to ensure that it will have good observability. Practical examples are shown below. If these measures are difficult to implement or there are any uncertainties about them, contact Seiko Epson.

- Applicable series: S1L50000, S1L30000, S1L9000F, S1X50000, S1K50000

- Prepare one scan enable input pin (SCANEN) as a dedicated input pin.

- Submit "trial data" to Seiko Epson one week prior to the release of the formal data. This trial data is necessary to preliminarily check your circuit prior to formal data-in, in order to increase the efficiency of work following formal data-in and achieve a high fault detection rate.

- The clock, reset, and set inputs of all flip-flops to be scanned must be controllable directly from the external pins.

- → If not controllable, configure a controllable circuit by attaching an ATPG test input pin (ATPGEN) separately from the SCANEN pin.

- → If the flip-flops are configured to have multiple clocks fed from external pins, make sure all of the flip-flops to be scanned basically operate with a single clock input when ATPGEN is active. However, if two or more of such circuit configurations exist, consult Seiko Epson.

Figure 2-10 Example of Processing of the Clock Line

- Circuit design using scan flip-flops in the original circuit is inhibited.

- Skew consideration for clock nets by Clock Tree Synthesis must be supported.

- I/O cells must be placed on the top hierarchical level.

- Do not use internal tri-state buses.

- → Correct the circuit to configure internal tri-state buses with multiplexers or the like. If it is unavoidable to use internal tri-state buses, use the ATPGEN pin to ensure that those bus circuits will not contend for bus control. However, because this measure is detrimental to increasing the fault detection rate, do not use such a circuit configuration if a high fault detection rate is desired.

Figure 2-11 Example of the Processing of Internal Tri-State Buses

- When using macro cells such as RAM, ROM, or megacells, include the flip-flops to be scanned in your circuit configuration before and after the input/output ports of those macro cells.

- → Without such a circuit configuration, fault detection before and after the macro cells may not be guaranteed.

- Avoid the use of MSI macros that include flip-flops (e.g., KT175 or KA161).

- → MSI cells are not scanned. If a high fault detection rate is desired, do not use MSI cells.

- The use of circuits that tend to cause racing, such as RS latches and differentiating circuits, as well as the use of asynchronous circuits, are inhibited.

- → When using such circuits, be sure to fix the circuit outputs with the ATPGEN pin. However, because this measure is detrimental to increasing the fault detection rate, do not use these circuits if a high fault detection rate is desired.

- Fix the latch cells with the ATPGEN pin to ensure that they will always be in a through state.

- → Because this measure is detrimental to increasing the fault detection rate, avoid using latch cells whenever possible if a high fault detection rate is desired.

- Make sure the bidirectional pins are set for input during scan shift mode.

- → If it is unavoidable for the bidirectional pins to be assigned for scan data input or scan data output, fix the pins for input or output, respectively.

Figure 2-12 Example of the Processing of Bidirectional Pins

- Fix the outputs of non-scanned flip-flops.

- → The outputs of MSI macros that include T-flip-flops or flip-flops, as well as those of non-scanned flip-flops, cause malfunction in the ATPG test pattern or hinder fault detection. Therefore, fix their outputs using the ATPGEN pin as much a as possible.

# (8) Other

- Depending on the number of scanned flip-flops, the number of gates increases by approximately 15% to 20% compared to that in the original circuit.

- The period required for DFT and ATPG depends on the circuit configuration and gate size. The DFT and ATPG work at Seiko Epson requires at least three days, which should be taken into account in your plan. (In some cases, depending on the circuit configuration, approximately 10 days may be required. Therefore, please carefully examine the presented materials when designing your circuit.)

- Prior to data-in, please send the "ATPG check sheet" and "external pin information" to Seiko

Epson. If circuit changes are required, you will be requested to make them. The test pattern

interfaced to Seiko Epson should include definitions of the external pins (e.g., ATPGEN and

SCANEN) for scan purposes.

- For ATPG support, CTS (Clock Tree Synthesis) is essential during placement and routing. Therefore, please submit the necessary information for Clock Tree Synthesis specified on page 15, along with said information.

# (9) ATPG check sheet

Please be sure to submit this sheet one week prior to data-in. Encircle the appropriate answer for each question.

| 1.  | Interface netlist format for Seiko Epson (gate level)                                                                           | Verilo     | g or | EDIF      |

|-----|---------------------------------------------------------------------------------------------------------------------------------|------------|------|-----------|

| 2.  | Are scan flip-flops used in the original circuit? (Note 1)                                                                      | Yes        | or   | <u>No</u> |

| 3.  | Is any macro cell, MSI cell, or intermittently oscillating cell used?                                                           | Yes        | or   | <u>No</u> |

| 4.  | If Yes, enter the cell name:                                                                                                    |            |      |           |

| 5.  | Is any internal tri-state bus used?                                                                                             | Yes        | or   | <u>No</u> |

| 6.  | Does any RS latch, differentiating circuit, or asynchronous circuit exist?                                                      | Yes        | or   | <u>No</u> |

| 7.  | Are latch cells used?                                                                                                           | Yes        | or   | <u>No</u> |

| 8.  | Are bidirectional pins included?                                                                                                | Yes        | or   | <u>No</u> |

| 9.  | Is there any clock that cannot be controlled directly from the outside?                                                         | Yes        | or   | <u>No</u> |

| 10. | Are there any reset/set pins for flip-flops or latch cells that cannot be controlled directly from the outside?                 | Yes        | or   | <u>No</u> |

| 11. | If you answered Yes to any of questions 3 through 10 above, is your circuit designed in conformity with the DFT rules? (Note 2) | <u>Yes</u> | or   | No        |

| 12. | Are I/O cells placed at the top level?                                                                                          | <u>Yes</u> | or   | No        |

| 13. | Are measures taken to correct the skew problems of clock nets by Clock Tree Synthesis?                                          | <u>Yes</u> | or   | No        |

Note 1: If Yes, please correct your circuit, as the circuit cannot be scanned.

Note 2: If No, please insert DFT, as the circuit cannot be scanned. In addition, if you would like to request DFT insertion by Seiko Epson because detailed circuit information is required in addition to this sheet, contact Seiko Epson.

# • External pin information

Enter the names of pins that match those in the pin arrangement table. The necessary pins vary with the circuit configuration. (Always be sure to specify the necessary pins.)

| <ul> <li>Clock input pins</li> </ul>           |                          |          |   |              |

|------------------------------------------------|--------------------------|----------|---|--------------|

| Pin name:                                      | Active edge: rise • fall |          |   |              |

| Pin name:                                      | Active edge: rise • fall |          |   |              |

| Pin name:                                      | Active edge: rise • fall |          |   |              |

| Pin name:                                      | Active edge: rise • fall |          |   |              |

| Pin name:                                      | Active edge: rise • fall |          |   |              |

| • Scan enable input pin (Note                  | 3)                       | Included | • | Not included |

| Pin name:                                      | Active level: High • Low |          |   |              |

| ATPG test input pin                            |                          | Included | • | Not included |

| Pin name:                                      | Active level: High • Low |          |   |              |

| Clear/preset input pin                         |                          | Included | • | Not included |

| Pin name:                                      | Active level: High • Low |          |   |              |

| <ul> <li>Other ATPG mode control pi</li> </ul> | ins                      | Included | • | Not included |

| a. Pin name:                                   |                          |          |   |              |

| Content of control, active                     |                          |          |   |              |

| :                                              |                          |          |   |              |

| b. Pin name:                                   | _                        |          |   |              |

| Content of control, active                     | level, etc.              |          |   |              |

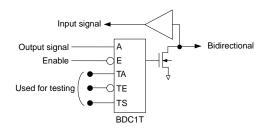

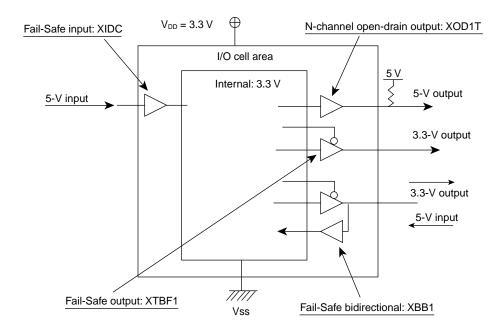

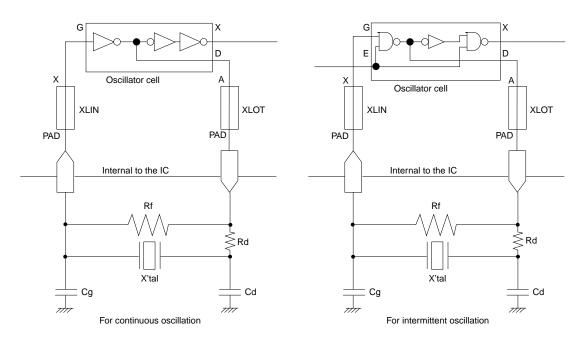

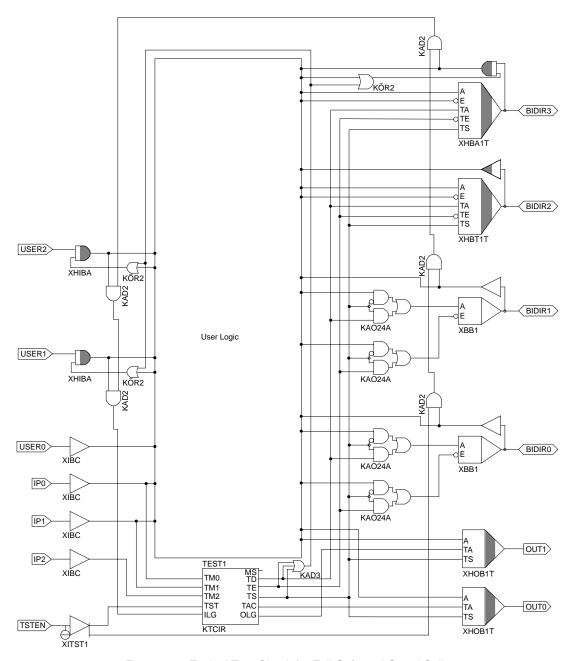

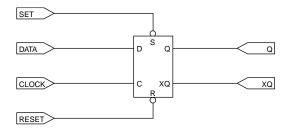

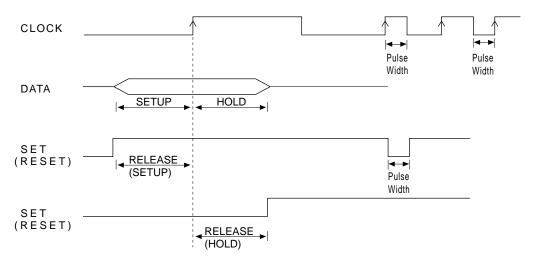

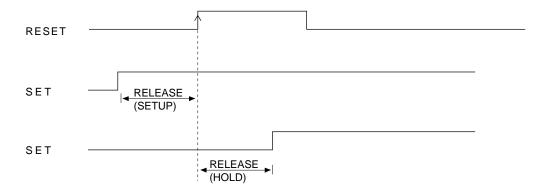

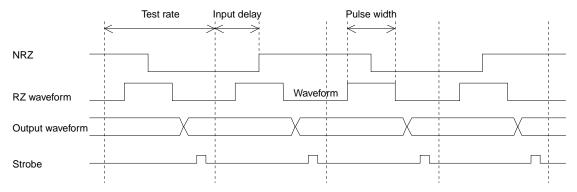

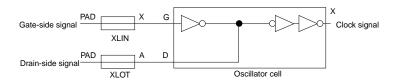

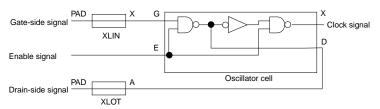

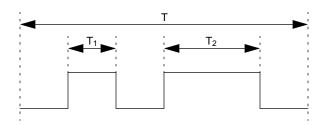

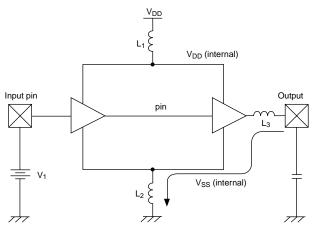

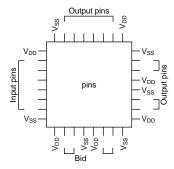

| :                                              |                          |          |   |              |